Mikrochips sind die zentralen Bauteile, aus denen alle modernen Computer bestehen. Sie begegnen uns nicht nur in Form von Prozessoren in PCs, an denen wir arbeiten, schreiben und surfen, sondern stecken auch in Waschmaschinen, Kühlschränken und Autos. Ohne sie würden die meisten Geräte des Alltagsgebrauchs gar nicht oder nur eingeschränkt funktionieren. Darum hat die ständige Entwicklung und Weiterentwicklung anwendungsspezifischer Mikrochips direkte Auswirkungen auf unser Leben. Mikrochips, die ausschließlich für eine spezielle Aufgabe gebaut werden, heißen Application-Specific Integrated Circuits (ASICs). Sie bestehen aus winzigen, einfachen Grundbausteinen, die auf kleinstem Raum zusammengeschaltet sind und im Zusammenspiel komplexe Funktionen ausführen können. Ihre große Stärke liegt darin, dass sie klein, schnell und verlässlich sind, und dass sie wenig Strom brauchen, um zu funktionieren. Ein Nachteil an ihnen ist allerdings, dass sie, einmal gebaut, nicht mehr verändert werden können: Wurde ein Mikrochip auf eine Platine gelötet oder geätzt, tut er immer das gleiche. Um neue Funktionen hinzuzufügen oder etwas zu ändern oder zu verbessern, muss der gesamte Chip neu gebaut werden. Das ist nicht nur aufwendig, sondern auch teuer.

In der Forschung wäre es praktisch, sich die positiven Eigenschaften von Mikrochips zunutze zu machen, denn durch ihre hohe Geschwindigkeit können sie Daten effektiv verarbeiten und Verfahren schnell ausführen. Doch da sich ebendiese Verfahren in der Entwicklung befinden, lohnt es sich finanziell und zeitlich kaum, für jede kleine Änderung, die ein Forscher ausprobieren möchte, einen neuen Mikrochip zu bauen. Daher findet die Entwicklung dieser Verfahren vornehmlich an gewöhnlichen Computern statt, die etwas langsamer sind und viel mehr Strom verbrauchen, da der Prozessor die gesamte Benutzeroberfläche und viele Hintergrundprozesse steuern muss.

FPGAs – eine echte Alternative

Eine vielversprechende Alternative zu ASICs sind Field-Programmable Gate Arrays (FPGAs). Dabei handelt es sich um eine spezielle Art von Mikrochips, die so gebaut sind, dass ihre Bauteile nicht „in Stein gemeißelt“ sind, sondern immer wieder neu und anders zusammengeschaltet werden können. Forscher*innen können einen Schaltplan erstellen, wie er auch einem echten ASIC zugrunde liegt. Doch anstatt einen echten ASIC bauen zu lassen, können sie ihn einfach auf einen FPGA laden, der die beschriebene Schaltung dann sofort ausführt. Dadurch ist es möglich, Schaltpläne laufend zu verbessern und immer wieder ohne großen Aufwand zu testen. Dieses Vorgehen ist nicht nur wesentlich schneller als der Bau mehrerer Versionen eines ASICs, sondern schont gleichzeitig Umweltressourcen und den Geldbeutel.

FPGAs eignen sich auch zur direkten Verwendung anstelle von ASICs: Wird ein FPGA in einem Auto verbaut, ist es möglich, im Nachhinein Aktualisierungen und Verbesserungen, z.B. neue Versionen von Fahrassistenzsystemen, auf den FPGA zu laden, ohne die Hardware komplett austauschen zu müssen. Dieser Eigenschaft verdankt der FPGA seinen Namensteil field-programmable, sprich „im Feld“ – also dem finalen Einsatzgebiet – programmierbar.

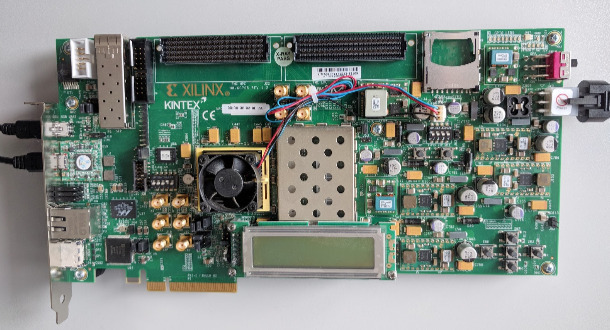

Dies ist ein FPGA-Board der Reihe Kintex von Xilinx. Der eigentliche FPGA ist ein quadratischer Chip, welcher unter dem Lüfter verbaut ist.

FPGAs für Maschinelles Lernen

FPGAs kommen bereits in den Bereichen Automobil, Video- und Audioverarbeitung sowie Medizin zum Einsatz. Auch für das Maschinelle Lernen bergen FPGAs mit ihrer Leistungsfähigkeit und Flexibilität großes Potenzial. So können sie Messungen in Echtzeit auswerten, indem sie diese mit Modellen wie Künstlichen Neuronalen Netzwerken klassifizieren. Dank ihres geringen Energieverbrauchs von häufig unter 1 Watt und ihrer hohen Verarbeitungsgeschwindigkeit eignen sie sich besonders gut zum Einsatz direkt am Ort, wo Daten entstehen, und wo wenig Platz oder Strom zur Verfügung steht. Auch können sie Verfahren erheblich beschleunigen, die auf normalen Rechnern zu langsam sind.

Diese Vorteile machte sich ein Forscherteam des ML2R zunutze. Die Forschenden entwickelten ein FPGA-basiertes System, das eine Klasse von Optimierungsproblemen (QUBO) schnell und mit einem geringen Ressourcenverbrauch lösen kann. Optimierungsprobleme bilden die Grundlage des Maschinellen Lernens. Hierbei wird aus vielen möglichen Lösungen diejenige gesucht, die nach einem festgelegten Kriterium die Beste ist. Aufgrund der Vielzahl möglicher Lösungen, die durchsucht werden müssen, würde ein normaler Computer oder gar ein Mensch theoretisch tausende von Jahren zur Lösung benötigen. Durch den Einsatz von FPGAs war es möglich, einen spezialisierten Algorithmus zu verwenden, der das QUBO-Problem lösen kann und dabei nur 1,5 Watt verbraucht. Das Forscherteam hat somit ein vielseitig einsetzbares Werkzeug entwickelt, das etliche maschinelle Lernverfahren beschleunigen kann.

Mikrochips und insbesondere FPGAs bieten eine interessante Plattform für Maschinelles Lernen, weil sie schnell, verlässlich und energieeffizient sind. Die Erforschung von Methoden, die klein genug sind, um auf Mikrochips zu passen, und dennoch schnell sind und garantiert korrekte und gute Ergebnisse liefern, ist ein wichtiges Themengebiet des Kompetenzzentrums ML2R. Die Integrierung dieser Technologie in unseren Alltag trägt dazu bei, dass maschinelles Lernen Einzug in unsere Alltagsgeräte hält und unser Leben auch in Zukunft immer weiter vereinfacht.

Mehr Informationen in den zugehörigen Publikationen:

Learning Bit by Bit: Extracting the Essence of Machine Learning

Sascha Mücke, Nico Piatkowski, Katharina Morik, Proceedings der Konferenz „Lernen, Wissen, Daten, Analysen“ (LWDA), 2019 PDF.